What is the Data Vortex® Switch?

The Data Vortex® switch is neither a mesh, nor a crossbar, nor a torus, nor a ring. Rather, it is an implementation independent self-routing dynamical system that eliminates the setting problem and is scalable due to small packets in a congestion-free network. It is not possible to achieve this using a crossbar-based network. The Data Vortex solution solves this problem by enabling a scalable, fine-grained parallel computer with high bandwidth, and low latency.

The parameterizable Data Vortex® has been and can be implemented in multiple RTL IP blocks in different ways for different needs. This RTL code may be written onto ASICs, FPGAs, and other accelerators to connect cores, compute elements, and/or accelerators.

Where can the Data Vortex play?

The Data Vortex topology can be implemented across multiple verticals within the ever-changing high-end, I.T. landscape. Experts across industry, government, and academia have identified such areas as:

- Shared Memory Nodes & Applications

- Big Data Graph Analytics appliances

- Consensus for Blockchain and Kubernetes

- Heterogenous computing environments

- High Performance Computing

- Data Centers

- Telecommunications (5G, DV-enabled Ethernet)

- Core-to-Core Communication on a Processor

- Chiplet Switch: Chiplets & Sockets

What are small packets good for?

- Active Messaging

- Internet of Things

- Big Data Graph Analytics

- BFT Consensus

- Artificial Intelligence & Machine Learning

- Sparse linear algebra

- GUPs

- Branching Algorithms

- All algorithms that require either massive data movement,

short packet movement, or non-deterministic data movement

Proven Results on the Data Vortex Network on Chip™

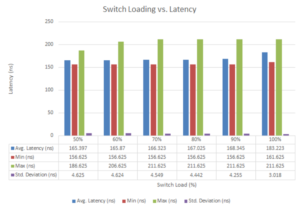

The DV NoC™, embedded within the network adapter's FPGA, is an exciting new hardware advancement that increases the performance of the Data Vortex network and allows users to add customer logic. Random Access on the NoC is exceeding 1.1 Billion 8-byte messages per second.

Switch Operation

- Data Vortex topology is based on rings arranged in levels. One ring on the top level, two rings on the next level down, and r rings on the bottom level where r is the radix of the switch.

- There is a collection of busses to carry data between the levels. These busses are arranged in such a way as to minimize contention.

- The logic of the network consists of decisions to stay on a ring or travel between rings.

- Data can flow out of a switch output port at a much higher rate than the injection rate enabling congestion free routing.

- The logic decisions are based on routing information in the packet header. There are no global switch controllers. The switch control logic time is hidden under the message passing.

For a large class of important problems, crossbar networks spend most of the time controlling the switches. The time spent in crossbar controller logic is the cause of the S-curves that result in the need for large packets (see Performance tab for visual representation). The large packets are the cause for poor performance for key scientific applications and extremely poor performance for active messaging and asynchronous computing.

An Orchestra of Beautiful Data Movement

"The intricate animation below of the Data Vortex topology is complemented with George Frideric's Handel’s Water Music. Handel premiered the orchestral piece on 17 July 1717 in a floating concert on the River Thames for King George I of Great Britain and his retinue. The Water Music and the Data Vortex are equally beautiful: one a musical representation of water's flow, the other a mathematical system born of fluid dynamics."

- Dr. Coke S. Reed, Inventor of the Data Vortex